This page is still under construction, I am using it as my

online notebook.

This page is still under construction, I am using it as my

online notebook. To Do It's time to finalize and sort the content on this page, but ...! ;-)

mkn, 2013, ;-)

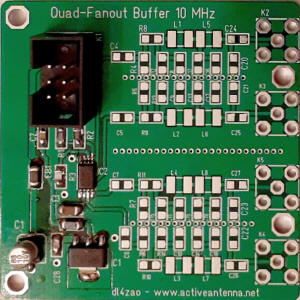

Signal-Verteiler, Fan-Out Buffer, Clock Buffer

- Eingang: Sinus- oder Digital-Signal

- Ausgang: Wave Form, Anzahl der Ausgänge, Entkopplung, Impedanz

- Einsatzgebiet, Verwendung, Anforderungen

- Passive, aktive Verteiler

Verbraucher:

Frequenzzähler, Transceiver, Signalgeneratoren, Spektrumanalyzer, Netzwerkanalyzer, PLL-Aufbereitungen, Oszillosgraph(2CH, als Vergleichssignal), ...

- 10-MHz-Referenzen in der Funktechnik

Teil 2

- Betriebskosten

- Genauigkeit, Stabilität, vergleich Rubidium-Normal mit GPSDO, Auswertung mittels Oszillographen, Allan-Deviation ADEV

Was fordern die Referenz-Frequenzeingänge der zu synchronisierenden Gerätschaften?

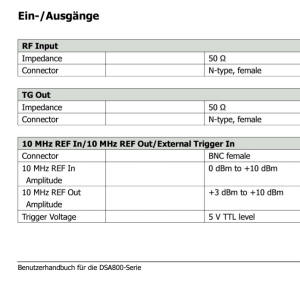

10 MHz reference frequency output power. 4 dBm, BNC-type female

External reference frequency input level range 10 MHz, 0 dBm to +20 dBm, BNC-type female

--> 0 dBm to +20 dBm

10 MHz reference output: 10 MHz, >0 dBm, BNC-type female, 50 Ω (nom.)

10 MHz reference input: 10 MHz, -5 to +10 dBm, BNC-type female, 50 Ω (nom.) Datenblatt

--> -5 to +10 dBm

0 dBm to +10 dBm

--> 0 dBm to +10 dBm

Quelle:

ICOM

Quelle:

ICOM

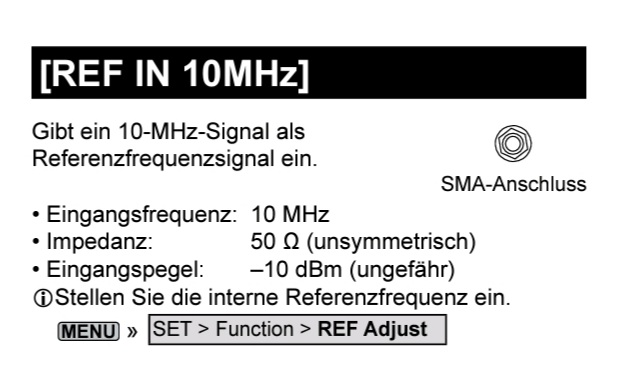

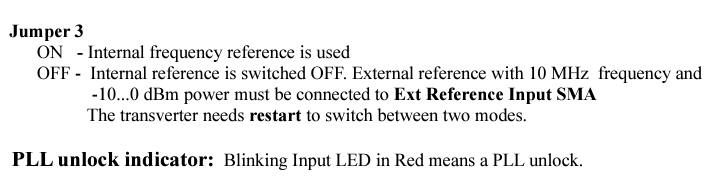

- 10

dBm; externes Dämpfungsglied verwenden oder internes erhöhen.

-> ca. - 10 dBm

- ICOM IC-

--> -10 ... 0 dBm

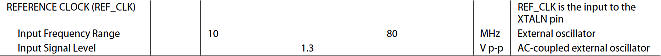

- External reference level, Vp-p 0.8..3.3 (+1..+13dBm at 50 Ohm), 10 MHz

--> +1..+13dBm

- Erweiterung für externen Referenzfrequenzeingang, Abschalten des internen XO

- 40 MHz, 25 MHz, 10 MHz ???

- Datenblatt AD9363

External REF-Input

VE4SW #11 Bild

1 MHz: 1 -5Veff

5 MHz: 0,5 -5Veff

Signaleingang: BNC, female

Eingangsimpedanz: unbekannt

Frequenzteilung durch Zwei

oder

vom sGPSDO 1 MHz abgreifen und über Pufferstufe bereitstellen

| Widerstand, 0805 | E24(5%) | ATT dB | |||

| 0 dB | NA | 0R | NA | 0 | |

| - 3 dB | 300 | 18 | 300 | 2,99 | |

| - 6 dB | 150 | 36 | 150 | 5,9 | |

| - 9 dB | 100 | 62 | 100 | 9,23 | |

| - 10 dB | 100 | 68 | 100 |

9,63 |

- Passive Verteiler

- Aktive Verteiler

- Zubehör, optionale Erweiterung zum sGPSDO

- Verwendung als eigenständige Baugruppe zum Verteilen von Signalen, analog oder digital

- Tiefpassfilter-Anpassung für die gewünschte Grenzfrequenz, z. B. für den 25-MHz-sGPSDO

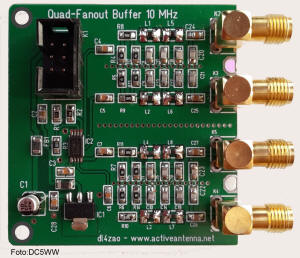

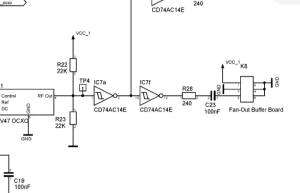

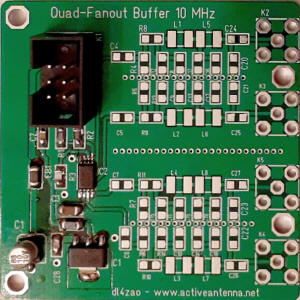

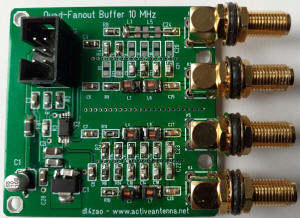

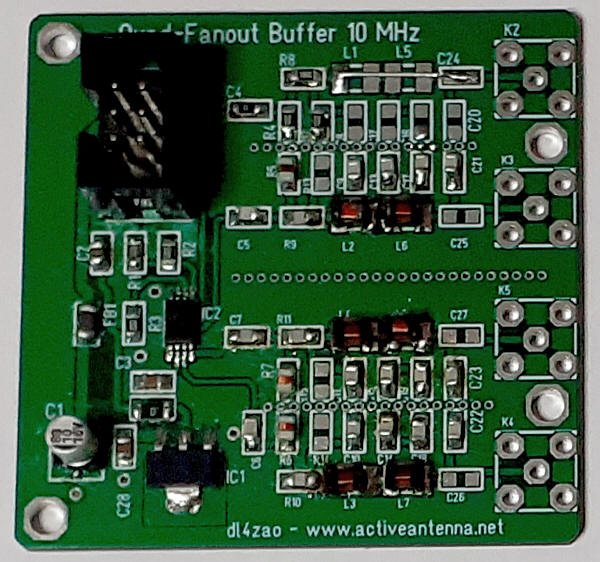

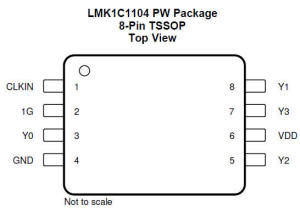

- Buffer IC, 4 Ausgänge

- 3 db-Dämpfungsglied

- 10 MHz-Tiefpass-Filter

- Ausgangspegel: ca. 6,5 dBm

- Oberwellenabstand:

- Betriebsspannung: 5 V

- Strom:

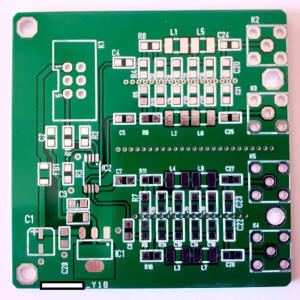

- Abmessungen der Leiterplatte: 53* 53 mm

- Bestückung der Platine, beachten sie die aktuelle Baumappe, V11 [06.01.21]

-> Download Manual und Baumappe (pdf)

-> https://www.reichelt.de/my/1718149

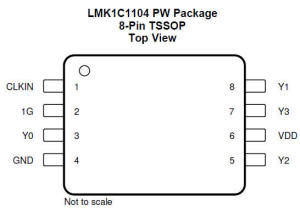

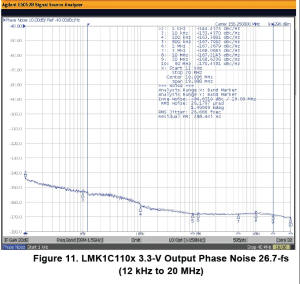

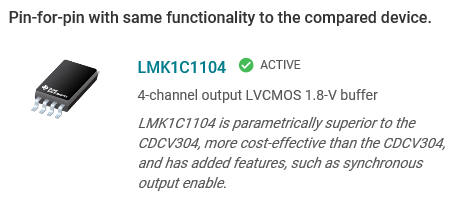

-> Digi-Key - LMK1C1104PWR

Position 8 (IC: LMK1C1104PWR)

- Datenblatt LMK1C110x 1.8-V, 2.5-V, and 3.3-V LVCMOS Clock Buffer Family datasheet(Rev. B)

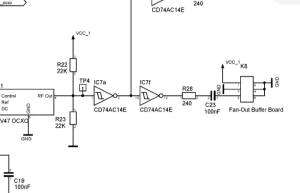

- sGPSDO; C23, 100nF, nicht bestücken und Brücke einfügen! [31.12.2020, mkn]

Ergebnis: Hierdurch erhält der Fan-Out-Buffer eine LVCMOS-Pegel gerechte Ansteuerung am Clockeingang des IC2.

- verbessertes Rechtecksignal an den IC2-Ausgängen

sGPSDO, PCb 2.37

- Abhilfe 10 uF X7R an IC1-OUT gegen Masse

- oder Ferrit-Perle FB2 überbrücken, oder entfernen und durch einen 0 Ohm Widerstand ersetzen

- ZLDO1117G33TA LDO-Regler, fest, 3,3 V, SOT-223-3, Datenblatt

Und hier in Kurzform einige Erinnerungen, Anmerkungen, Notizen und Erfahrungen von Anwendern [mkn]

- Einsatz, überprüft, OK, mkn

- Aufbauvariante: IC-TP-3-dB-Dämpfungsglied(dem TP nachgeordnet!), C23 ist noch nicht gebrückt!

- PCB aus der Null-Serie

- LQH3C 1,0µ: SMD-Induktivität, 1210, Murata Chip Coil, 1,0µ bei reichelt elektronik

Datenblatt Artikelnummer des Herstellers LQH32CN1R0M23L

I= 5mA, ohne Ansteuerung

I= 55 mA mit Ansteuerung, alle 4 Ausgänge 50 Ohm Last

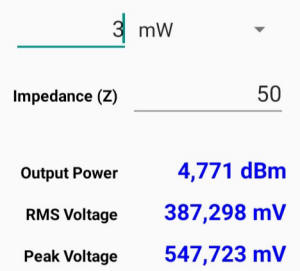

Ausgangspegel der obigen Aufbauvariante

Pout= 3mW, d.h. 4,8 dbm

Oberwellenabstand @ 20 MHz= -30 dBc

Oberwellenabstand @20MHz, eigentlich mehr erwartet, gelöst; C23

- Filter

- Kurvenform des 10 MHz Signals

- Rechteck 50:50% Tastverhältnis?

- HCMOS-Ausgangssignal des OCXO

- OCXO CTI OSC5A2B02 Duty Cycle 45/55 %

- Aufbau eines Buffers nach BM V09 , DL7UKM

- sGPSDO; C23, 100nF, nicht bestücken und Brücke einfügen! [31.12.2020, mkn]

Ergebnis: Hierdurch erhält der Fan-Out-Buffer eine LVCMOS-Pegel gerechte Ansteuerung am Clockeingang des IC2.

- verbessertes Rechtecksignal an den IC2-Ausgängen

DL7UKM, SMD-Lötversuche, hi.

- Aufbau der ersten Filtersektion zum K4, ohne Dämpfungsglied

Ausgangsleistung= 9,5 dBm,

9,5 dbm-> 8,9 mW, 668 mVrms, 944 mVp, 1888 mVpp

- danach erst die Induktivitäten

3 dB-Dämpfungsglieder am Ausgang des TP

- Pout 4,3 mW [zweiter Aufbau 4,1 mW]

- TP um eine Sektion erweitert

- 1.Oberwelle -55 dBc [zweiter Aufbau -50 dBc]

4,3 mW -> 6,3 dBm, 464 mVrms, 656 mVpk

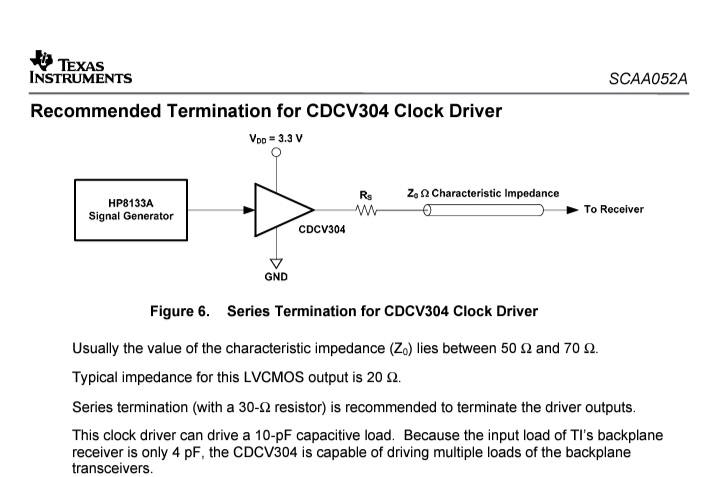

Source: TI

- Abhilfe 10 uF X7R an IC1 OUT gegen Masse, der verfügbare 1206 ist etwas zu lang, aber noch händelbar.

- oder Ferrit-Perle FB2 überbrücken, oder entfernen und durch einen 0 Ohm Widerstand ersetzen

- ZLDO1117G33TA LDO-Regler, fest, 3,3 V, SOT-223-3, Datenblatt

Auszug aus dem Datenblatt

"Stability

The ZLDO1117 requires an output capacitor as part of the device frequency compensation. As part of its improved performance over industry standard 1117 the ZLDO1117 is suitable for use with MLCC (Multi Layer Ceramic Chip) capacitors. A minimum of 4.7μF ceramic X7R, 4.7μF tantalum, or 47 μF of aluminum electrolytic is required. The ESR of the output capacitor should be less than 0.5Ω. Surface mount tantalum capacitors, which have very low ESR, are available from several manufacturers. When using MLCC capacitors avoid the use of Y5V dielectrics."

Ersten Signalverteiler aufgebaut. Mein erstes SMD-Board....

Ansteuerung: sGPSDO, PCB V1.0, C23 gebrückt, via Pfostenstecker und Verbindungskabel 20 cm

K2: digitaler Ausgang, 3 dB-Dämpfungsglied

K3: Sinus-Ausgang, 0 dB DG, TP

Output: 9,5 dBm, 8,9 mW, 668 mVrms, 944 mVp, 1888 mVpp

K5: Sinus-Ausgang, 3 dB DG, TP

Output: 6,5 dBm, 4,5 mW, 473 mVrms, 668 mVp, 1336 mVpp

K4: Sinus-Ausgang, 3 dB DG, TP, Output: 6,5 dBm

Output: 6,5 dBm, 4,5 mW, 473 mVrms, 668 mVp, 1336 mVpp

Ausgangspunkt der Bestückung: BM v 09

Ergänzt: mit 10 uF, 16 V, X7R, 1206, über Ausgangs-Pin IC1 zur Masse

Last: 50 Ohm

- Achtung, Gestaltung der SMA-f-Ausgänge

- gerade oder Winkel-Buchsen?

- Montage der PCB, Horizontal oder Vertikal?

- Montage der PCB parallel zur Rückwand

Verwendung des CDCV304 TI

CDCV304

Ja, das war

unser eigentliches Anliegen, die Verwendung aktuellster

Bauelemente. Und nun geht es einen Schritt zurück in Zeiten der Pandemie

und der fehlenden Verfügbarkeit des IC's.

Ja, das war

unser eigentliches Anliegen, die Verwendung aktuellster

Bauelemente. Und nun geht es einen Schritt zurück in Zeiten der Pandemie

und der fehlenden Verfügbarkeit des IC's.

- Eigenart Subharmonische von 5 MHz

OCXO verwendet einen Oberton-Quarz von 5 MHz mit anschließendem aktiven Frequenz-Verdoppler

Modifizierte Bestückung, DL7UKM

- Verwendung als Verteiler eines UNI-OCXO mit MORION MV89A

bestückt

- Dämpfungsglieder für K3, K4, K5 entfallen

- Pads C6, R6, R10 für einen Hochpass genutzt, R14 entfällt

- neu: C6, R10 -> C= pF

R6 -> L= nH

- AC-Ansteuerung

-QUADRUPLE DIFFERENTIAL LINE DRIVER, 5 V

- Each driver has a TTL-compatible input buffered to reduce current and minimize loading.

- The outputs are capable of source or sink currents of 48 mA.

- The MC3487 is designed for optimum performance when used with the MC3486 quadruple line receiver.

Pout > 10mW

NB3N551DR2GOSCT-ND

- Datenblatt

Leider nicht PIN kompatibel!

Leider nicht PIN kompatibel!- To Do

- Kein Referenzfrequenz-Eingang vorhanden und nun?

- FUNKAMATEUR 2021 H8., S.611

- NRD-525, KW-Empfänger

- 12,8 MHz TCXO, +/- 3ppm

296-8450-1-ND

Drawing, Bilder

Modification